arm内存系统,ARM内存系统概述

时间:2024-10-29 来源:网络 人气:

ARM内存系统概述

ARM架构因其高效能、低功耗的特点,被广泛应用于嵌入式系统、移动设备以及服务器等领域。ARM内存系统作为其核心组成部分,对于整个系统的性能和稳定性至关重要。本文将详细介绍ARM内存系统的架构、工作原理以及相关技术。

ARM内存系统架构

ARM内存系统主要包括以下几个部分:内存控制器、缓存、内存管理单元(MMU)和存储器。以下是各部分的功能概述:

内存控制器:负责管理内存的读写操作,包括地址译码、数据传输等。

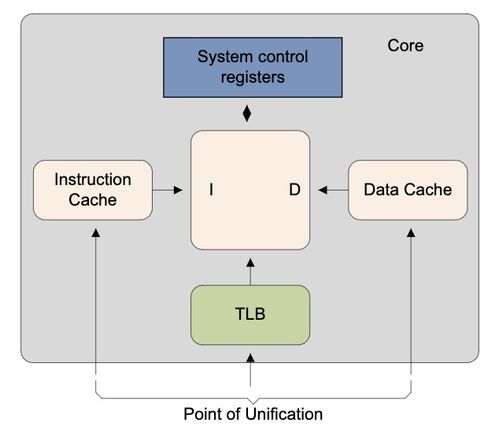

缓存:用于提高内存访问速度,包括指令缓存和数据缓存。

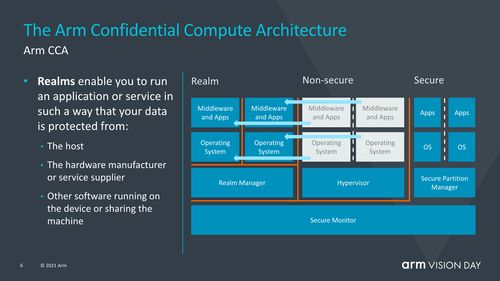

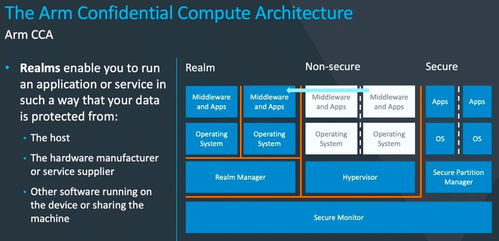

内存管理单元(MMU):负责实现虚拟内存管理,将虚拟地址转换为物理地址。

存储器:包括RAM、ROM等,用于存储程序和数据。

ARM缓存技术

缓存技术是ARM内存系统的重要组成部分,主要包括以下几种:

指令缓存(I-Cache):用于存储指令,提高指令执行速度。

数据缓存(D-Cache):用于存储数据,提高数据访问速度。

一级缓存(L1 Cache):位于CPU内部,访问速度最快。

二级缓存(L2 Cache):位于CPU外部,容量大于L1 Cache。

三级缓存(L3 Cache):在某些高端处理器中存在,容量更大。

ARM内存管理单元(MMU)

ARM内存管理单元(MMU)是实现虚拟内存管理的关键部件,其主要功能包括:

地址转换:将虚拟地址转换为物理地址。

内存保护:限制对内存的访问权限。

内存映射:将设备或文件映射到内存地址空间。

ARM内存一致性

在多核处理器系统中,内存一致性是保证数据正确性的关键。ARM内存一致性主要涉及以下几个方面:

地址映射变化:确保地址映射的一致性。

指令缓存一致性:保证指令执行的正确性。

直接内存访问(DMA)操作:确保DMA操作的正确性。

其他内存一致性问题:如缓存一致性、写缓冲区一致性等。

ARM内存系统优化技术

缓存优化:合理配置缓存大小、行大小和替换策略,提高缓存命中率。

内存管理优化:合理配置内存分区、内存映射和内存保护,提高内存利用率。

指令重排:优化指令执行顺序,提高指令执行效率。

多级缓存一致性协议:保证多核处理器系统中内存的一致性。

ARM内存系统作为ARM架构的核心组成部分,对于整个系统的性能和稳定性至关重要。本文介绍了ARM内存系统的架构、工作原理以及相关技术,旨在帮助读者更好地理解和优化ARM内存系统。

教程资讯

教程资讯排行